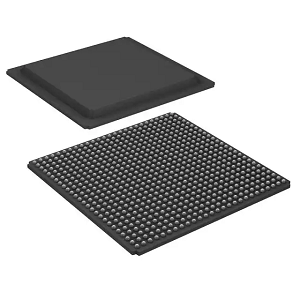

XC7Z030-2FFG676I – Integrerede kredsløb (IC'er), indlejrede, system på chip (SoC)

Produktegenskaber

| TYPE | BESKRIVELSE |

| Kategori | Integrerede kredsløb (IC'er) |

| Mfr | AMD |

| Serie | Zynq®-7000 |

| Pakke | Bakke |

| Produktstatus | Aktiv |

| Arkitektur | MCU, FPGA |

| Kerne processor | Dual ARM® Cortex®-A9 MPCore™ med CoreSight™ |

| Flash størrelse | - |

| RAM størrelse | 256 KB |

| Periferiudstyr | DMA |

| Forbindelse | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Fart | 800MHz |

| Primære attributter | Kintex™-7 FPGA, 125K logiske celler |

| Driftstemperatur | -40°C ~ 100°C (TJ) |

| Pakke/etui | 676-BBGA, FCBGA |

| Leverandørenhedspakke | 676-FCBGA (27x27) |

| Antal I/O | 130 |

| Basisproduktnummer | XC7Z030 |

Dokumenter og medier

| RESSOURCETYPE | LINK |

| Dataark | Zynq-7000 Oversigt over alle programmerbare SoC |

| Produkttræningsmoduler | Driver Series 7 Xilinx FPGA'er med TI Power Management Solutions |

| Miljøoplysninger | Xiliinx RoHS-certifikat |

| Udvalgt produkt | Alle programmerbare Zynq®-7000 SoC |

| PCN Design/Specifikation | Mult Dev Material Change 16/Dec/2019 |

| Errata | Zynq-7000 Errata |

Miljø- og eksportklassifikationer

| EGENSKAB | BESKRIVELSE |

| RoHS-status | ROHS3 kompatibel |

| Moisture Sensitivity Level (MSL) | 4 (72 timer) |

| REACH-status | REACH upåvirket |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Application Processor Unit (APU)

Nøglefunktionerne ved APU inkluderer:

• Dual-core eller single-core ARM Cortex-A9 MPCores.Funktioner forbundet med hver kerne omfatter:

• 2,5 DMIPS/MHz

• Driftsfrekvensområde:

- Z-7007S/Z-7012S/Z-7014S (trådbinding): Op til 667 MHz (-1);766 MHz (-2)

- Z-7010/Z-7015/Z-7020 (trådbinding): Op til 667 MHz (-1);766 MHz (-2);866 MHz (-3)

- Z-7030/Z-7035/Z-7045 (flip-chip): 667 MHz (-1);800 MHz (-2);1 GHz (-3)

- Z-7100 (flip-chip): 667 MHz (-1);800 MHz (-2)

• Mulighed for at arbejde i enkelt processor, symmetrisk dual processor og asymmetrisk dual processor modes

• Enkelt og dobbelt præcision flydende komma: op til 2,0 MFLOPS/MHz hver

• NEON-mediebehandlingsmotor til SIMD-understøttelse

• Thumb®-2 understøttelse af kodekomprimering

• Niveau 1 caches (separat instruktion og data, 32 KB hver)

- 4-vejs sæt-associativ

- Ikke-blokerende datacache med understøttelse af op til fire udestående læse- og skrivefejl hver

• Integreret hukommelsesstyringsenhed (MMU)

• TrustZone® til drift i sikker tilstand

• Accelerator Coherency Port (ACP) interface, der muliggør sammenhængende adgang fra PL til CPU hukommelsesplads

• Unified Level 2 cache (512 KB)

• 8-vejs sæt-associativ

• TrustZone aktiveret for sikker drift

• Dual-ported, on-chip RAM (256 KB)

• Tilgængelig med CPU og programmerbar logik (PL)

• Designet til lav latensadgang fra CPU'en

• 8-kanals DMA

• Understøtter flere overførselstyper: hukommelse-til-hukommelse, hukommelse-til-perifer, perifer-til-hukommelse og scatter-samler

• 64-bit AXI-grænseflade, der muliggør DMA-overførsler med høj kapacitet

• 4 kanaler dedikeret til PL

• TrustZone aktiveret for sikker drift

• Grænseflader med dobbelt registeradgang fremtvinger adskillelse mellem sikre og ikke-sikre adgange

• Afbrydelser og timere

• General interrupt controller (GIC)

• Tre vagthunde-timere (WDT) (én pr. CPU og en system-WDT)

• To tredobbelte timere/tællere (TTC)

• CoreSight fejlfinding og sporing af Cortex-A9

• Programmer sporingsmakrocelle (PTM) til instruktion og sporing

• Cross trigger interface (CTI), der muliggør hardware breakpoints og triggers