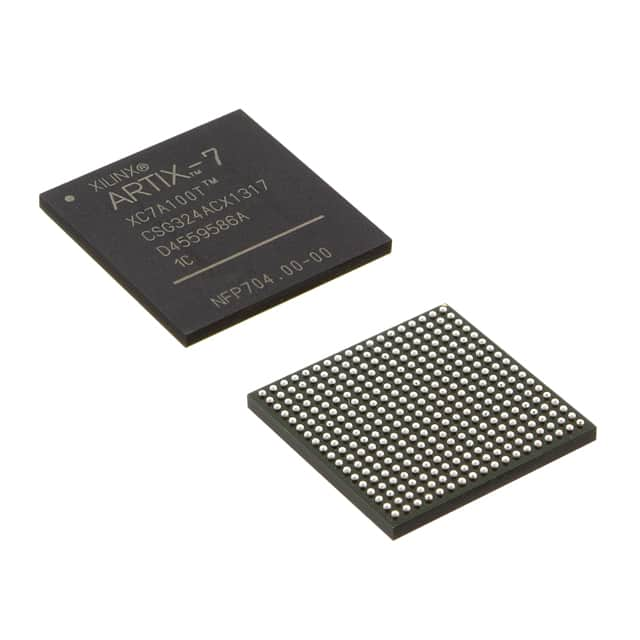

Original IC-chip programmerbar XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

Produktegenskaber

| TYPE | BESKRIVELSE |

| Kategori | Integrerede kredsløb (IC'er) |

| Mfr | AMD Xilinx |

| Serie | Virtex® UltraScale™ |

|

| Boks |

| Standard Pakke | 1 |

| Produktstatus | Aktiv |

| Antal LAB'er/CLB'er | 316620 |

| Antal logiske elementer/celler | 5540850 |

| Samlet RAM Bits | 90726400 |

| Antal I/O | 1456 |

| Spænding – Forsyning | 0,922V ~ 0,979V |

| Monteringstype | Overflademontering |

| Driftstemperatur | -40°C ~ 100°C (TJ) |

| Pakke/etui | 2892-BBGA, FCBGA |

| Leverandørenhedspakke | 2892-FCBGA (55×55) |

| Basisproduktnummer | XCVU440 |

Brug af FPGA'er som trafikprocessorer til netværkssikkerhed

Trafik til og fra sikkerhedsenheder (firewalls) er krypteret på flere niveauer, og L2-kryptering/dekryptering (MACSec) behandles ved linklagets (L2) netværksnoder (switches og routere).Behandling ud over L2 (MAC-laget) omfatter typisk dybere parsing, L3-tunneldekryptering (IPSec) og krypteret SSL-trafik med TCP/UDP-trafik.Pakkebehandling involverer parsing og klassificering af indgående pakker og behandling af store trafikmængder (1-20M) med høj gennemstrømning (25-400Gb/s).

På grund af det store antal computerressourcer (kerner), der kræves, kan NPU'er bruges til relativt højere hastighedspakkebehandling, men lav latens, højtydende skalerbar trafikbehandling er ikke mulig, fordi trafikken behandles ved hjælp af MIPS/RISC-kerner og planlægning af sådanne kerner baseret på deres tilgængelighed er vanskelig.Brugen af FPGA-baserede sikkerhedsapparater kan effektivt eliminere disse begrænsninger af CPU- og NPU-baserede arkitekturer.

Sikkerhedsbehandling på applikationsniveau i FPGA'er

FPGA'er er ideelle til inline sikkerhedsbehandling i næste generations firewalls, fordi de med succes opfylder behovet for højere ydeevne, fleksibilitet og drift med lav latens.Derudover kan FPGA'er også implementere sikkerhedsfunktioner på applikationsniveau, som yderligere kan spare computerressourcer og forbedre ydeevnen.

Almindelige eksempler på applikationssikkerhedsbehandling i FPGA'er omfatter

- TTCP aflastningsmotor

- Matching af regulære udtryk

- Asymmetrisk kryptering (PKI) behandling

- TLS-behandling

Næste generations sikkerhedsteknologier, der bruger FPGA'er

Adskillige eksisterende asymmetriske algoritmer er sårbare over for kompromittering fra kvantecomputere.Asymmetriske sikkerhedsalgoritmer såsom RSA-2K, RSA-4K, ECC-256, DH og ECCDH er de mest påvirkede af kvanteberegningsteknikker.Nye implementeringer af asymmetriske algoritmer og NIST-standardisering er ved at blive udforsket.

Aktuelle forslag til postkvantekryptering omfatter Ring-on-Error Learning (R-LWE)-metoden til

- Public Key Cryptography (PKC)

- Digitale signaturer

- Nøgleskabelse

Den foreslåede implementering af offentlig nøglekryptografi omfatter visse velkendte matematiske operationer (TRNG, Gaussisk støjsampler, polynomieaddition, binær polynomisk kvantifier division, multiplikation osv.).FPGA IP for mange af disse algoritmer er tilgængelig eller kan implementeres effektivt ved hjælp af FPGA-byggeklodser, såsom DSP- og AI-motorer (AIE) i eksisterende og næste generation af Xilinx-enheder.

Denne hvidbog beskriver implementeringen af L2-L7-sikkerhed ved hjælp af en programmerbar arkitektur, der kan implementeres til sikkerhedsacceleration i edge/access-netværk og næste generations firewalls (NGFW) i virksomhedsnetværk.